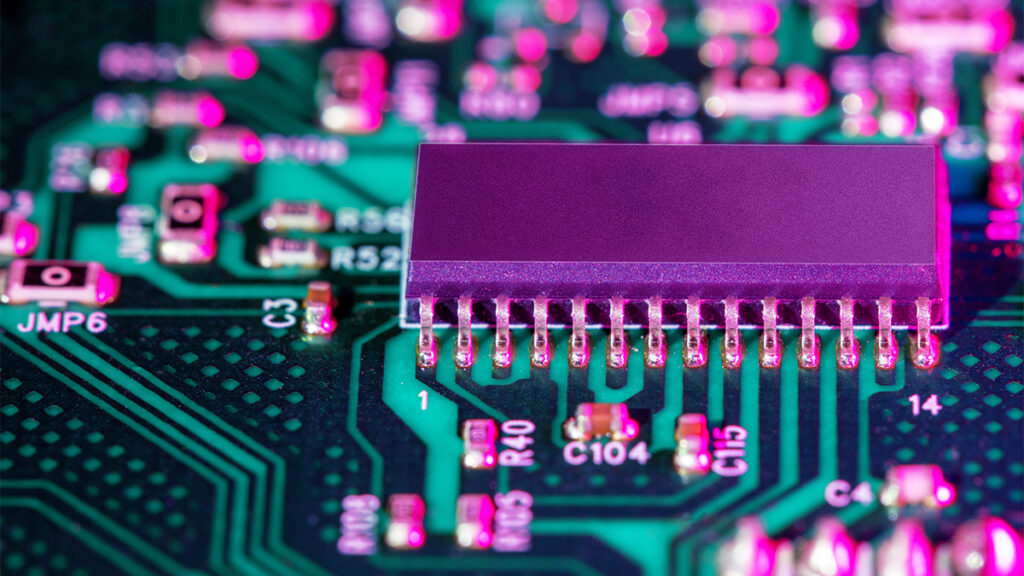

GlobalFoundries’ MIPS To Buy ARC IP Business from Synopsys

Today sees a bold move to bring two key processor architectures, MIPS and ARC, under one umbrella, as GlobalFoundries announced it is buying Synopsys’ ARC processor IP solutions business, including its teams of engineers and designers, and integrating it into the MIPS business.

GlobalFoundries’ MIPS To Buy ARC IP Business from Synopsys Read More »