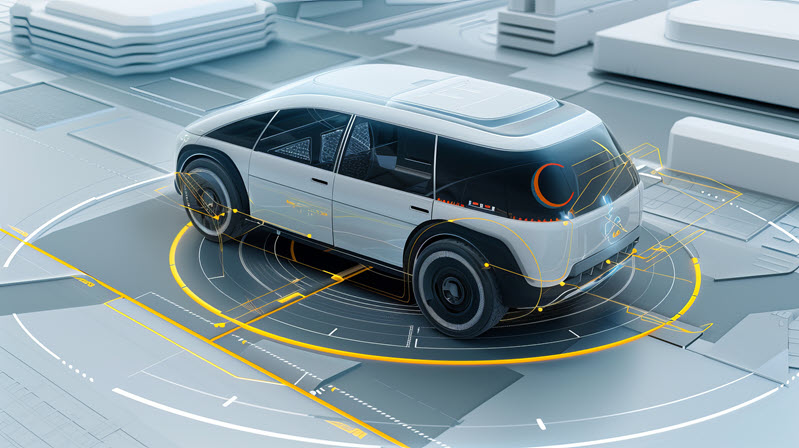

Meet MIPS S8200: Real-Time, On-Device AI for the Physical World

Physical AI is the ability for machines to sense their environment, think locally, act safely, and communicate quickly without waiting on the cloud. In safety-critical scenarios like driver assistance or industrial robotics, milliseconds matter. That’s why MIPS’ edge-first approach focuses on ultra-low latency, low power, and cost-efficient inference delivered by its Atlas portfolio—and specifically the […]

Meet MIPS S8200: Real-Time, On-Device AI for the Physical World Read More »