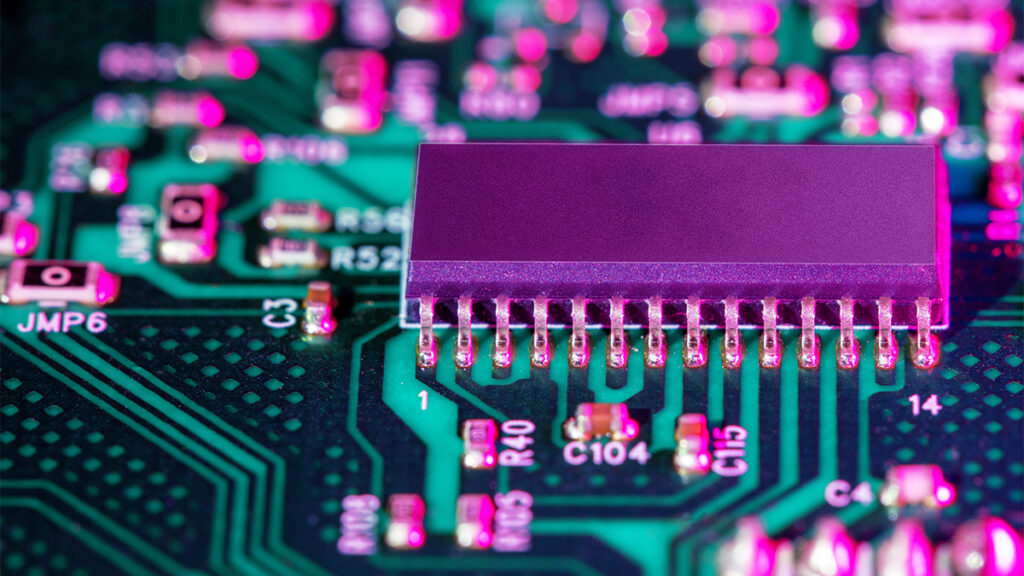

Sameer Wasson: ‘MIPS Will Not Become A Silicon Company’

Last time I sat down with Sameer Wasson, CEO of IP company MIPS. He told me the company had absolutely no plans to make chips. Fast forward a year and MIPS has launched a silicon platform, Atlas.

Sameer Wasson: ‘MIPS Will Not Become A Silicon Company’ Read More »