# Cautionary Statement

This presentation may contain forward-looking statements concerning MIPS™, a GlobalFoundries company (MIPS) such as, the opportunities for continued growth based on MIPS product portfolio and growing demand for autonomous and real-time computing; MIPS ability to position itself for long-term growth and value creation; the features, functionality, performance, availability, timing and expected benefits of future MIPS products. In some cases, forward-looking statements can be identified by terms such as "forecast," "outlook," "may," "will," "remains," "to be," "plans," "believes," "expects," "anticipates," "intends," "targets," "projects," "contemplates," "believes," "estimates," "aims," "predicts," "potential," "seeks," "attempts," "poised," "continues," and similar expressions and the negatives of those terms and similar expressions.

If applicable, this presentation and any accompanying materials may contain estimates and other statistical data made by independent parties relating to market size, growth and other industry data. This information involves a number of assumptions and limitations, and you are cautioned to not give undue weight to such estimates. MIPS has not independently verified the statistical and other industry information contained in this presentation and any accompanying materials. Accordingly, MIPS cannot and does not guarantee the accuracy or completeness of this information.

Any performance, power, efficiency, or other product or competitive claims are estimates based on MIPS internal projections and are subject to change. Results may vary based on final product specification, use case, workload, implementation, and other related factors outside of consideration in these statements.

All rights reserved. All copyrights, logos and trademarks belong to their respective owners.

Copyright © MIPS™ a GlobalFoundries company, 2026.

# Physical AI Is Built On MIPS

## Overview

Jan 14<sup>th</sup> 2026

# AI is Transforming the Physical World

Basic

Intelligence

Basic Autonomy

Industrial

Intelligence

Autonomous

Systems

Multi-Purpose

Intelligence

Past

Future

# The Compute Challenge of Physical AI

Dynamic, Unpredictable Environments

**SENSE**

**THINK**

**ACT**

**COMMUNICATE**

Gather

Environment Data

Autonomous

Decision Making

Movement &

Action

Data & Status

Updates

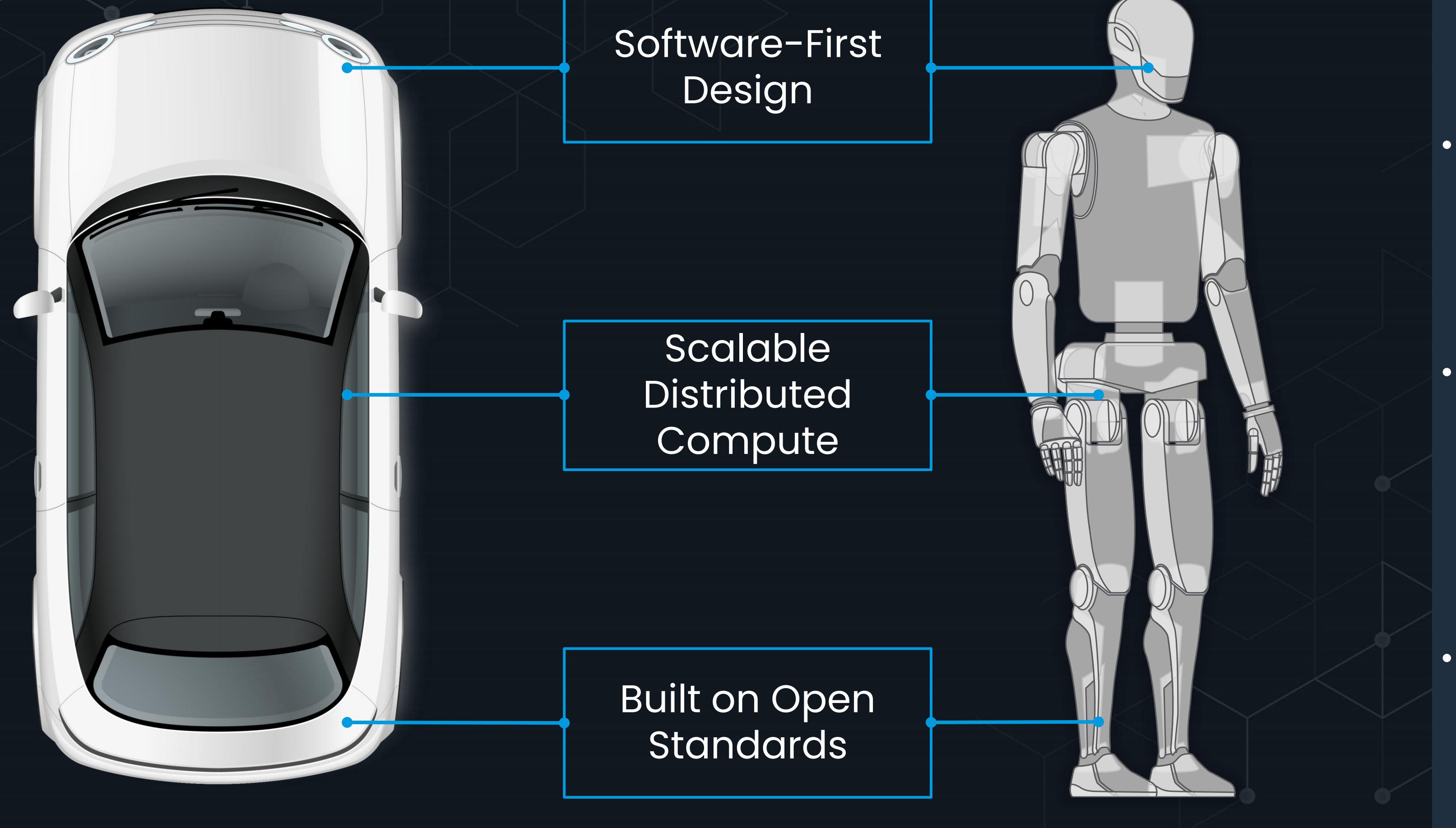

# The Growth of AI to the Edge Changes Design Approach

## Software-Defined Architectures

- Software-First Design

- Standardized Compute Blocks

- Application Specific Optimization

- Standards-Based Technology

- Open, Modular ISA

- Common code base

- Shared Toolchain

- Commercial Vendor Support

- Scalable, Distributed Compute

- Workload Focused SoCs

- Software Enhanced Function

# Software-First Design: Software & Tools

Workload

Modeling with

Virtual Core IP

Software/

Hardware

Co-Design

Digital Twin

Lifecycle

Management

## Software Guided Intelligence

- Earlier insights for smarter designs

- Atlas Explorer virtual platform

- Atlas IP Core Models

- Platform Design Insights

- Cycle Accurate Modeling

- AI-Enhanced SW/HW Co-design

- Application Optimization

- Code Migration & Tuning

- Workload Focused Toolchains

- AI-Powered Software Tuning & Optimization

# Standards Based Technology: RISC-V Processor IP

Profile

Compliant

Processor

Modular ISA

Extensions

Application

Specific

Instructions

## Open, Modular, Extensible

- Standardized Programming Model

- Easy to Adopt & Use

- Common Code Bases

- Commercial & Open-Source Toolchains

- Software Defined Functionality

- Base Profile Compliant with RISC-V Extensions

- Application Specific Instructions

- Workload Tuned Architectures

# Scalable Distributed Compute

Less Compute

More Compute

## Scalable Autonomous Edge Architectures

- Reduced use of low-volume, high-cost ASICs in single applications

- Differentiated Product Design

- Re-use platform architectures in adjacent markets

- Economy of Scale

- Supply Chain Management

- Reduced Time-to-Market

- Shared Development Costs

- Higher Quality

- Simpler Support

# Mapping Physical AI to Compute Engines

Breaking Down the Workload Into Engines

**SENSE**

**THINK**

**ACT**

**COMMUNICATE**

Multi-stream Data

Aggregation & Control

On-Device

Transformer &

Language Model

Inference

Real-Time Control &

Low-Latency Event

Processing

Low-Latency, High-

Throughput, Secure Data

Orchestration

Compute-Dense Applications

Processor Clusters

Software-First AI Accelerator for

Transformer & Language Model

Workloads

High-Performance

Real-Time

Microcontrollers

Multi-Threaded Data

Movement Engines

**MIPS IP:** **P8700**

**S8200**

**M8500**

**I8500**

# MIPS Atlas Portfolio of RISC-V Processor IP

|                                    | Transportation                                                                                                                            | Robotics                                                                                                                                 | Embedded                                                                                                                                          | Technology                                                                                                                                                                                                                                                          |

|------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>M8500</b><br><b>ACT</b>         | <ul style="list-style-type: none"><li>• Embedded Control Unit</li><li>• On-board Battery Management</li><li>• Traction Invertor</li></ul> | <ul style="list-style-type: none"><li>• Control Loops</li><li>• Safety Domain</li></ul>                                                  | <ul style="list-style-type: none"><li>• Intelligent Power Management</li><li>• Energy Infrastructure</li><li>• SSD Channel Controller</li></ul>   | <b>High-Performance 32-bit Microcontroller</b> <ul style="list-style-type: none"><li>• Field-Oriented Control Algorithm Acceleration</li><li>• Functional Safety (DCLS, ASIL-D, ASIL-B)</li><li>• Real-Time Multithreading (4-Threads per Core)</li></ul>           |

| <b>I8500</b><br><b>COMMUNICATE</b> | <ul style="list-style-type: none"><li>• Zonal Gateway</li></ul>                                                                           | <ul style="list-style-type: none"><li>• Industrial Gateway</li></ul>                                                                     | <ul style="list-style-type: none"><li>• SSD Storage Controller</li><li>• Communications Infrastructure</li><li>• Intelligent Networking</li></ul> | <b>Embedded 64-bit Data Orchestration Processor</b> <ul style="list-style-type: none"><li>• Native Linux/RTOS/Bare metal OS support</li><li>• 4-Threads per Core, 6-Core Clusters</li><li>• Scales up to 384 Clusters</li><li>• Native big-Endian support</li></ul> |

| <b>P8700</b><br><b>SENSE</b>       | <ul style="list-style-type: none"><li>• Data Movement Engine (ASIL)</li></ul>                                                             | <ul style="list-style-type: none"><li>• Data Movement Engine (SIL)</li></ul>                                                             | <ul style="list-style-type: none"><li>• Data Movement Engine for Smart NIC/DPU</li><li>• Embedded Applications Processor</li></ul>                | <b>Performance Applications Processor</b> <ul style="list-style-type: none"><li>• 2-Threads per Core</li><li>• 64-bit Out-of-Order Pipeline</li><li>• Functional Safety (ASIL-B)</li><li>• Multicore Cluster scaling</li></ul>                                      |

| <b>S8200</b><br><b>THINK</b>       | <ul style="list-style-type: none"><li>• ADAS (Bird's Eye View; OMS/DMS; LKA; Traffic Sign Recognition, etc.)</li></ul>                    | <ul style="list-style-type: none"><li>• Predictive Maintenance</li><li>• Real-time Monitoring</li><li>• Vision/Language Models</li></ul> | <ul style="list-style-type: none"><li>• On-Device Modern AI Inference</li></ul>                                                                   | <b>Embedded Neural Processing Unit</b> <ul style="list-style-type: none"><li>• Support Transformer &amp; Language Models</li><li>• Area-dense with class-leading TOPS/w</li><li>• RISC-V Vector &amp; Matrix extension support</li></ul>                            |

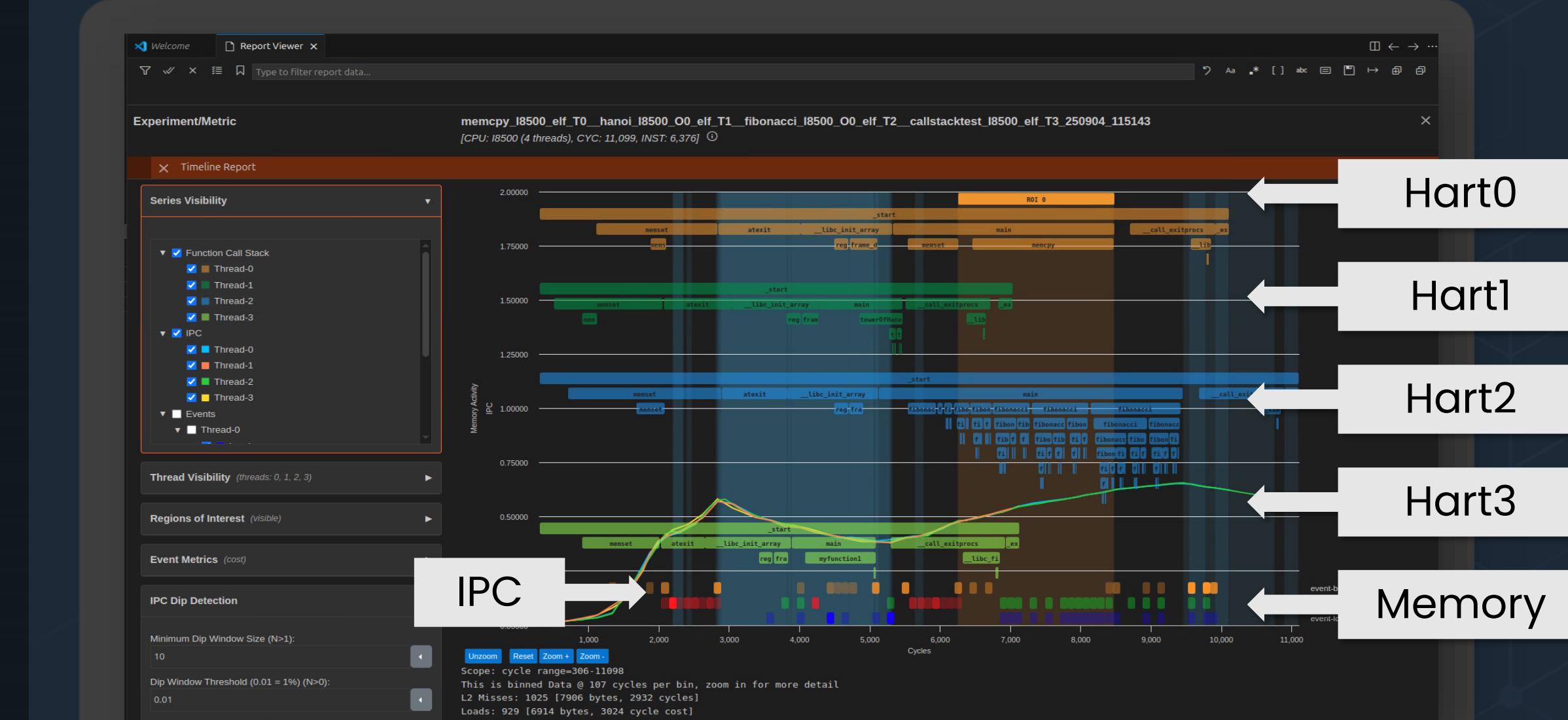

# Earlier Insights | Smarter Designs

## Software-First Design

Atlas Explorer virtual platform for

Atlas Core Models

## Shift-Left Development

Start your software optimization before

RTL, FPGA, and silicon availability

## Platform Design Insights

Branch trends, load/store activity, ALU usage,

register pressure, cache locality, IPC & more

## MIPS Atlas Explorer for Visual Studio Code

# MIPS + GF Bring Physical AI to Life

## MIPS Workload driven IP & Design

Software-First

Processor IP

Design

Modular

Workload

Extensions

Processor IP

Optimized for

Physical AI

Open Standard

Instruction Set

Architecture

Architecture Influences Technology

Technology Enables Architecture

Optimized Process Technologies

World's most

feature-rich FinFET

FDX: Lowest power,

highest integration

Advanced

Packaging: Size,

power,

performance

Microarchitecture optimizations for efficiency in

ultra-low power process technology

Ultra-low power process technology

(up to 50% benefit PPA)

Data paths & pipelines to process;

Key algorithm acceleration

Industry leading integrated RF & embedded memory

(RRAM, MRAM)

Software migration & application development

Dedicated I/O devices enabling dense SoC integration

# Autonomous Edge Applications

## Transportation

Automotive

Driver

Assistance

Systems

Self-flying

Uncrewed

Aircraft

Autonomous

Mobile Robot

## Robotics

Automated

Assembly

Warehouse &

Logistics

Humanoid

Robot

## Embedded

Intelligent

Motor Control

Network Data

Orchestration

Power

Infrastructure

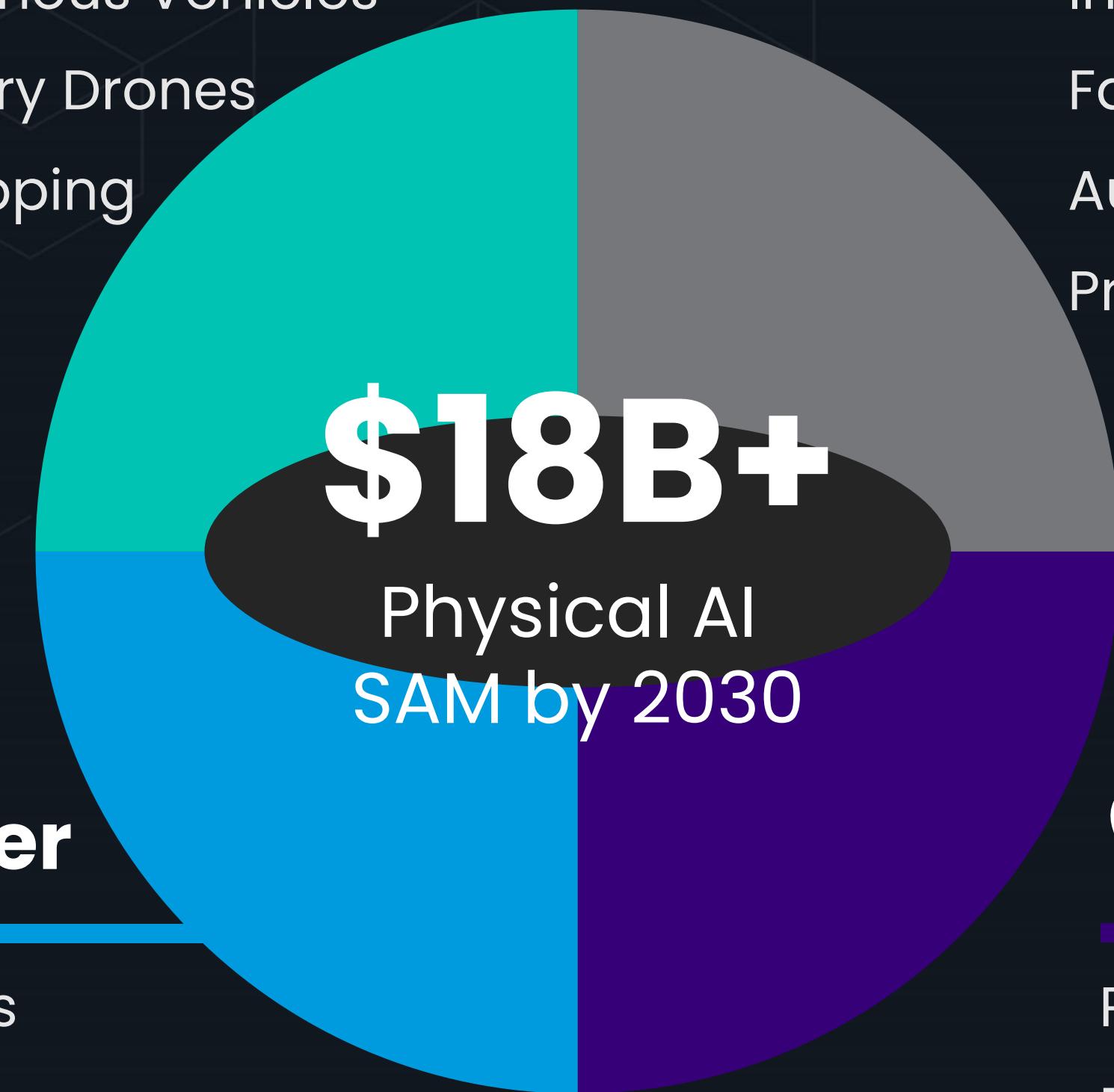

# A Significant & Expanded Market Opportunity

## Transportation

- Personal Autonomous Vehicles

- Logistics & Delivery Drones

- Autonomous Shipping

- Robotaxis

## Consumer

- Humanoid Robots

- Smart Glasses

- Smart Home Devices

- AI-Enabled AR/VR

## Industrial

- Industrial Robots

- Factory & Agricultural Cobots

- Autonomous Defense Systems

- Predictive Maintenance Systems

## Medical

- Robotic Surgeries

- Diagnostic Wearables

- Medical Smart Sensors

- Smart Drug Delivery Systems

## Enhanced Business Model

### Differentiated Technology

### Custom Silicon

### IP Licensing & Royalties

### Software

**Accretive to GF's

Long-Term Goals**

# Thank You

Press@MIPS.com

# Endnote

## Cautionary Statement

This presentation may contain forward-looking statements concerning MIPS™, a GlobalFoundries company (MIPS) such as, the opportunities for continued growth based on MIPS product portfolio and growing demand for autonomous and real-time computing; MIPS ability to position itself for long-term growth and value creation; the features, functionality, performance, availability, timing and expected benefits of future MIPS products. In some cases, forward-looking statements can be identified by terms such as "forecast," "outlook," "may," "will," "remains," "to be," "plans," "believes," "expects," "anticipates," "intends," "targets," "projects," "contemplates," "believes," "estimates," "aims," "predicts," "potential," "seeks," "attempts," "poised," "continues," and similar expressions and the negatives of those terms and similar expressions.

If applicable, this presentation and any accompanying materials may contain estimates and other statistical data made by independent parties relating to market size, growth and other industry data. This information involves a number of assumptions and limitations, and you are cautioned to not give undue weight to such estimates. MIPS has not independently verified the statistical and other industry information contained in this presentation and any accompanying materials. Accordingly, MIPS cannot and does not guarantee the accuracy or completeness of this information.

Any performance, power, efficiency, or other product or competitive claims are estimates based on MIPS internal projections and are subject to change. Results may vary based on final product specification, use case, workload, implementation, and other related factors outside of consideration in these statements.

All rights reserved. All copyrights, logos and trademarks belong to their respective owners.

Copyright © MIPS™ a GlobalFoundries company, 2026.