# MIPS RV64 P8700/P8700-F Multiprocessing System Programmer's Guide

Revision 1.81 February 13, 2025 This document contains information that is proprietary to MIPS Tech, LLC and MIPS' affiliates, as applicable, ("MIPS"). If this document is obtained pursuant to a MIPS Open license, the sole licensor under such license is MIPS Tech, LLC. This document and any information therein are protected by patent, copyright, trademarks and unfair competition laws, among others, and are distributed under a license restricting their use. MIPS has intellectual property rights, including patents or pending patent applications in the U.S. and in other countries, relating to the technology embodied in the product that is described in this document. Any distribution release of this document may include or be accompanied by materials developed by third parties. Any copying, reproducing, modifying or use of this information (in whole or in part) that is not expressly permitted in writing by MIPS or an authorized third party is strictly prohibited. Any document provided in source format (i.e., in a modifiable form such as in FrameMaker or Microsoft Word format) may be subject to separate use and distribution restrictions applicable to such document. UNDER NO CIRCUMSTANCES MAY A DOCUMENT PROVIDED IN SOURCE FORMAT BE DISTRIBUTED TO A THIRD PARTY IN SOURCE FORMAT WITHOUT THE EXPRESS WRITTEN PERMISSION OF, OR LICENSED FROM, MIPS. MIPS reserves the right to change the information contained in this document to improve function, design or otherwise.

MIPS does not assume any liability arising out of the application or use of this information, or of any error or omission in such information. DOCUMENTATION IS PROVIDED "AS IS" AND ANY WARRANTIES, WHETHER EXPRESS, STATUTORY, IMPLIED OR OTHERWISE, INCLUDING BUT NOT LIMITED TO THE IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT, ARE EXCLUDED, EXCEPT TO THE EXTENT THAT SUCH DISCLAIMERS ARE HELD TO BE LEGALLY INVALID IN A COMPETENT JURISDICTION. Except as expressly provided in any written license agreement from MIPS or an authorized third party, the furnishing or distribution of this document does not give recipient any license to any intellectual property rights, including any patent rights, that cover the information in this document.

Products covered by and information contained this document are controlled by U.S. export control laws and may be subject to the expert or import laws in other countries. The information contained in this document shall not be exported, reexported, transferred, or released, directly or indirectly, in violation of the law of any country or international law, regulation, treaty, Executive Order, statute, amendments or supplements thereto. Nuclear, missile, chemical weapons, biological weapons or nuclear maritime end uses, whether direct or indirect, are strictly prohibited. Should a conflict arise regarding the export, reexport, transfer, or release of the information contained in this document, the laws of the United States of America shall be the governing law.

U.S Government Rights – Commercial software. Government users are subject to the MIPS Tech, LLC standard license agreement and applicable provisions of the FAR and its supplements.

MIPS, MIPS II, MIPS III, MIPS IV, MIPS V, MIPS32, MIPS64, microMIPS32, microMIPS64, MIPS-Based, MIPSsim, CorExtend, IASim, microAptiv, microMIPS, proAptiv, SOC-it, and MIPS Open are trademarks or registered trademarks of MIPS in the United States and other countries. All other trademarks referred to herein are the property of their respective owners.

MIPS Document Number: MD01502

# **Table of Contents**

| Chapter 1: Architecture Overview                              |    |

|---------------------------------------------------------------|----|

| 1.1: Product Overview                                         |    |

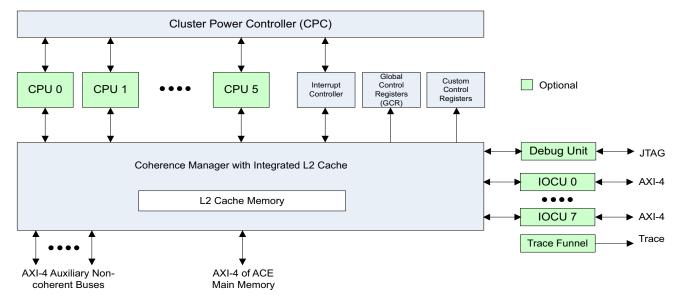

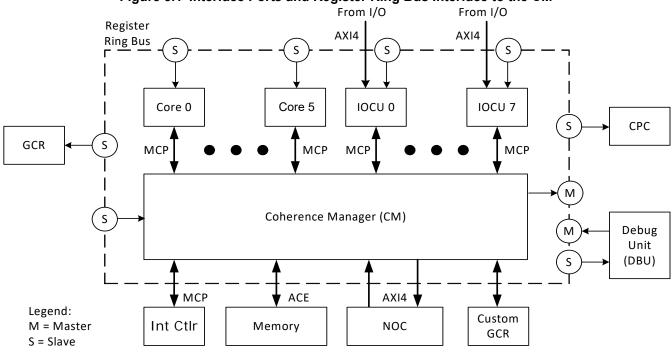

| 1.1.1: Single-Cluster Configuration                           | 13 |

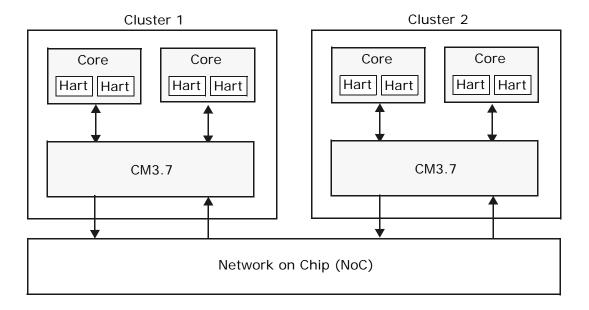

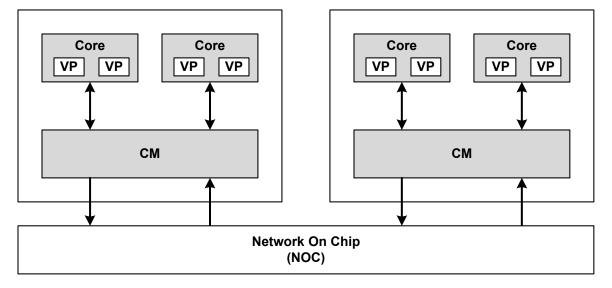

| 1.1.2: Multi-Cluster Configuration                            | 14 |

| 1.2: P8700-F Features                                         |    |

| 1.2.1: MIPS Out-of-Order Multithreading                       | 16 |

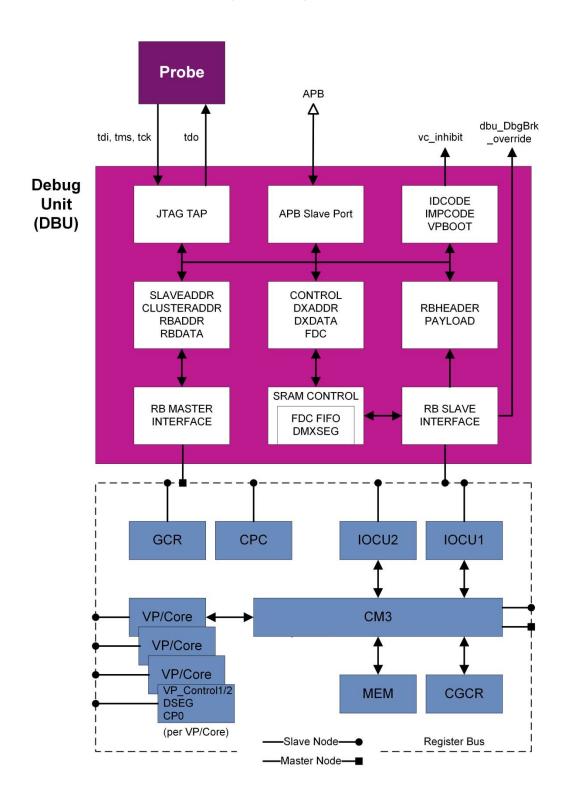

| 1.2.2: Hybrid Debug                                           |    |

| 1.3: P8700/P8700-F Privileged Architecture                    |    |

| 1.4: Functional Safety                                        |    |

| 1.5: System-level Features                                    |    |

| 1.6: CPU Core-Level Features                                  |    |

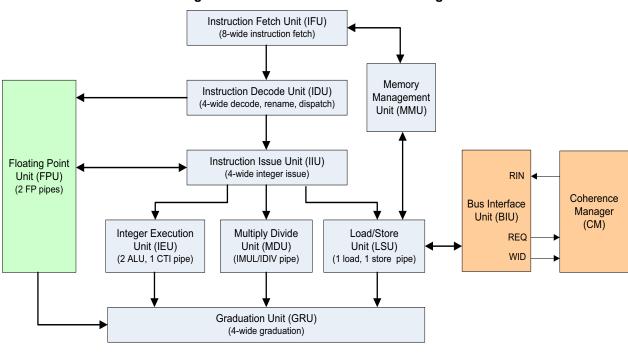

| 1.7: P8700-F Core Block Diagram                               |    |

| 1.8: MIPS Software Tools                                      |    |

| 1.8.1: RISC-V Linux                                           |    |

| 1.8.2: MIPS RISC-V SDK                                        | 19 |

| 1.8.3: Compilers                                              |    |

| 1.8.4: Boot Loader                                            |    |

| 1.9: Performance Considerations                               |    |

| 1.10: Additional Information                                  |    |

|                                                               |    |

| Chapter 2: Memory Management Unit                             | 21 |

| 2.1: Overview                                                 |    |

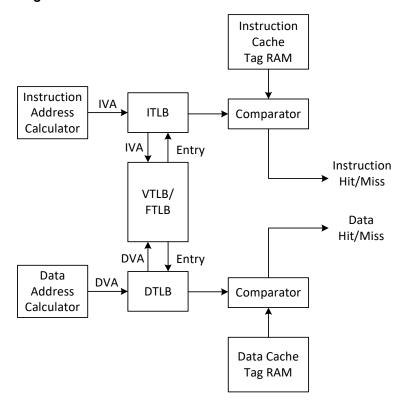

| 2.1.1: TLB Types                                              |    |

| 2.1.2: Instruction TLB (ITLB)                                 |    |

| 2.1.3: Data TLB (DTLB)                                        |    |

| 2.1.4: Variable Page Size TLB (VTLB)                          |    |

| 2.1.4.1: VTLB Organization                                    |    |

| 2.1.5: Fixed Page Size TLB (FTLB)                             |    |

| 2.2: TLB ECC Errors.                                          |    |

| 2.3: MIPS TLB Exception Handling                              |    |

| 2.4: TLB Duplicate Entries                                    |    |

| 2.5: TLB Instructions.                                        |    |

| 2.6: Shared FTLB Translations                                 |    |

| 2.7: Hardware Table Walker                                    |    |

| 2.8: MMU Programming                                          |    |

| 2.0. Willio i rogiuming                                       | 20 |

| Chapter 3: Caches                                             | 26 |

| 3.1: Cache Configurations                                     |    |

| 3.2: LR and SC Instruction Considerations                     |    |

| 3.3: Cache Subsystem Overview                                 |    |

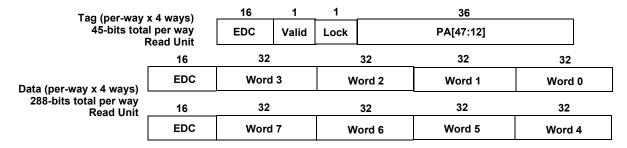

| 3.3.1: L1 Instruction Cache                                   |    |

| 3.3.1.1: Level 1 Instruction Cache Error Detection            |    |

|                                                               |    |

| 3.3.1.2: L1 Instruction Cache Organization                    |    |

| 3.3.1.4: L1 Instruction Cache Error Types                     |    |

| 3.3.1.5: L1 Instruction Cache Replacement Policy              |    |

|                                                               |    |

| 3.3.1.6: FENCE.I Instruction Usage                            |    |

| 3.3.3: Level 1 Data Cache Error Checking and Correction (ECC) |    |

|                                                               |    |

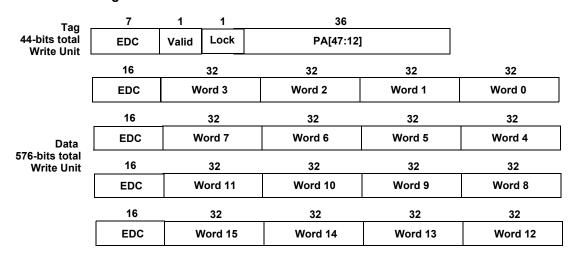

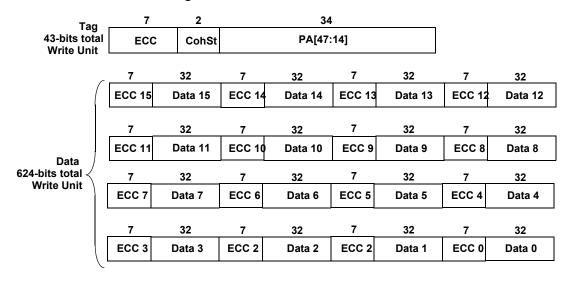

| 3.3.3.1: L1 Data Cache Organization                           | 33 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 3.3.3.2: L1 Data Cache Load/Store Operations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                        |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 3.3.3.3: L1 Data Cache Error Types                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 33                                                                                                                                     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 3.3.3.4: Store Operations Less than 32-bits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 3.3.3.5: Examples of L1 Data Cache ECC Errors                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 33                                                                                                                                     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 3.3.4: L1 Data Cache Replacement Policy                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 3.3.5: L1 Data Cache Memory Coherence Protocol                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                        |

| 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 3.3.6: Load/Store Bonding                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 35                                                                                                                                     |

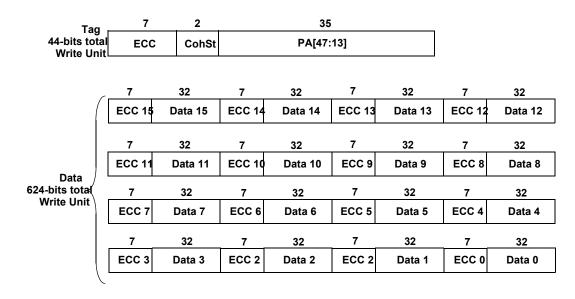

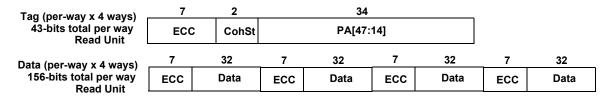

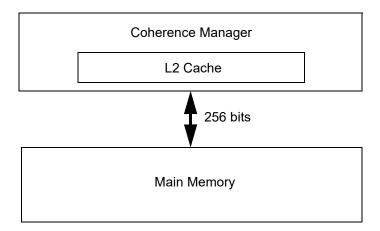

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 3.3.7: L2 Cache                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 3.3.8: L2 Cache General Features                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                        |

| 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 3.3.9: Overview of the AXI Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 3.3.9.1: AXI Channels                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 3.3.9.2: Read Operations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 3.3.9.3: Write Operations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 3.3.9.4: AXI Memory Bus Ordering                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 3.3.10: Cache Instructions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Cache Coherency                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | L2 Cache Initialization Options                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 3.5.1: Automatic Hardware Cache Initialization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | L2 Cache Flush, Burst, and Abort                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                        |